# Lesson 2: The Central Processing Unit (CPU)

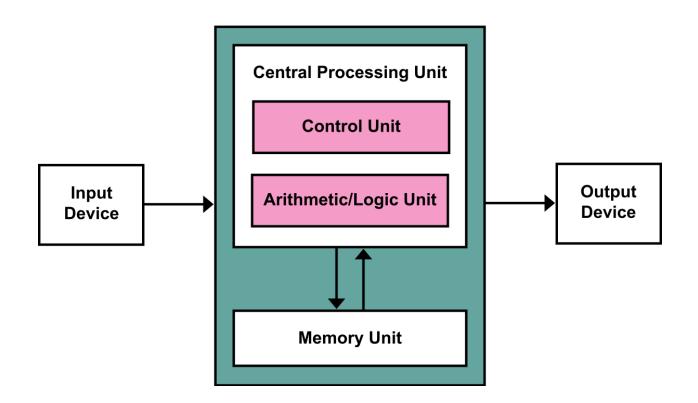

The Central Processing Unit (CPU) is often referred to as the brain of the computer due to its critical role in interpreting and executing instructions from both software and hardware components. It's where most calculations take place, making it a vital element in determining the overall performance of a computer system. In essence, the CPU is responsible for executing a sequence of stored instructions called a program. This process involves performing basic arithmetic, logical, control, and input/output (I/O) operations specified by the instructions. The efficiency and speed with which these tasks are carried out directly affect the computer's capability to perform tasks, from simple document editing to complex scientific calculations.

### Key Components of the CPU

The CPU can be dissected into several key components, each with a specific function, working together to process data and instructions. The major parts include:

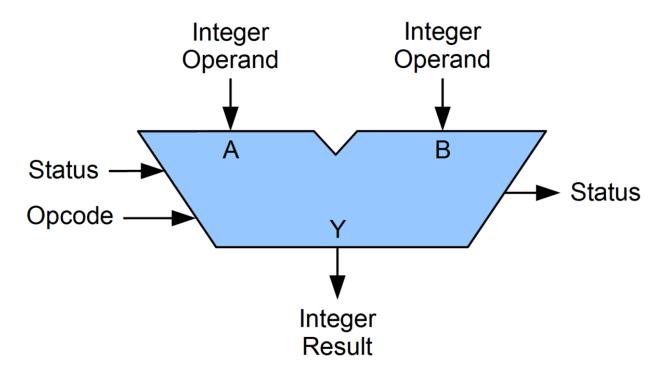

**Arithmetic Logic Unit (ALU):** The ALU is responsible for carrying out all arithmetic and logical operations. Arithmetic operations include basic calculations such as addition, subtraction, multiplication, and division, while logical operations involve comparisons, such as determining if one value is equal to, greater than, or less than another. The ALU is a fundamental component that directly impacts the CPU's ability to perform mathematical and decision-making processes efficiently.

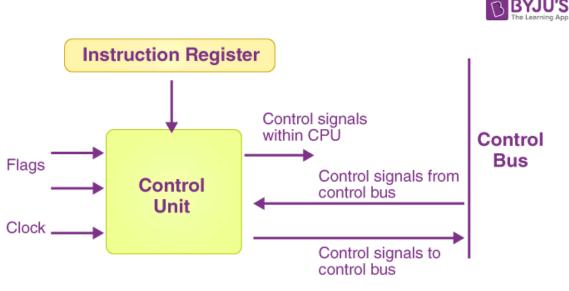

**Control Unit (CU):** The Control Unit acts as the conductor, directing the operation of the processor. It tells the computer's memory, ALU, and input/output devices how to respond to the instructions that have been sent to the processor. It does not execute program instructions; rather, it directs other parts of the system to do so. The CU fetches the instruction from memory, decodes it to determine what action is required, and then executes it by directing the relevant parts of the computer to carry out the instruction.

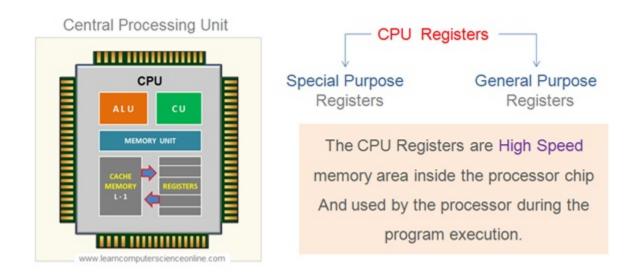

**Registers:** Registers are small, high-speed storage locations within the CPU used to hold temporary data and instructions that are being used by the CPU. There are various types of registers, including the accumulator (for storing intermediate arithmetic and logic results), index registers (for memory addressing), and general-purpose registers (for various functions). The speed of registers is essential for the CPU's performance, as they provide the quickest access to data and instructions for the processor.

Together, these components allow the CPU to perform the complex series of actions that constitute the processing of data and instructions. The design and capability of these components determine the efficiency, speed, and power of the CPU, and by extension, the computer as a whole. Advances in CPU technology, such as increases in clock speed, the introduction of multiple cores to process instructions in parallel, and improvements in the architecture and design of these key components, have significantly enhanced computer performance over time.

## **CPU** Architecture

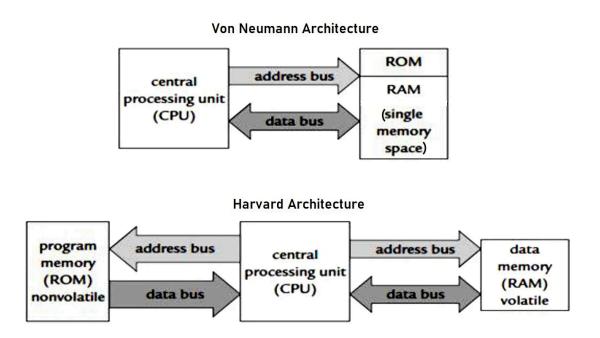

CPU architecture plays a crucial role in determining how a computer operates, processes data, and executes instructions. Two fundamental architectures form the backbone of most computer systems: Von Neumann Architecture and Harvard Architecture. Each has its unique approach to handling instructions and data within the computing system.

### Von Neumann Architecture

The Von Neumann Architecture, also known as the Princeton Architecture, is a computer design model that uses a single memory space for storing both instructions and data. This architecture is based on the concept introduced by John Von Neumann in 1945, which outlines a system where the CPU operates sequentially, fetching instructions from memory, decoding them, and then executing them. The key feature of this architecture is its simplicity and flexibility, as it allows the same memory and bus to be used for both instructions and data, reducing the complexity and cost of the system.

In a Von Neumann system, the process of fetching instructions and data from the same memory space can lead to a bottleneck, known as the "Von Neumann bottleneck." This occurs because both instruction fetch and data operations need to access the same memory over the same set of buses, which can limit the speed at which instructions are executed.

#### Harvard Architecture

In contrast, the Harvard Architecture is designed with separate storage and signal pathways for instructions and data. This means that the CPU can simultaneously

access instructions and read/write data, potentially doubling the system's throughput. The separation allows for instructions and data to be fetched in parallel, significantly speeding up the execution process compared to the Von Neumann Architecture.

The Harvard Architecture is often used in specialized systems where performance and efficiency are critical, such as digital signal

processing (DSP) and embedded systems. By having separate memories for data and instructions, the Harvard design can optimize the flow and processing of information within the CPU, leading to faster and more efficient computation.

#### Comparison

The primary difference between the Von Neumann and Harvard architectures lies in their approach to memory organization and access. While the Von Neumann model is celebrated for its simplicity and flexibility, making it suitable for general-purpose computing, it is constrained by the bottleneck that arises from using a single path for both data and instructions. On the other hand, the Harvard Architecture offers improved performance through parallel access to instructions and data but at the cost of increased system complexity and potentially higher manufacturing costs due to the need for two separate memory units.

In practice, many modern CPUs implement a modified Harvard Architecture, where the system appears to have a single memory for data and instructions (like Von Neumann) but internally maintains separate caches for instructions and data. This approach aims to combine the flexibility and simplicity of the Von Neumann Architecture with the performance benefits of the Harvard Architecture, addressing the limitations of both models.

## The CPU's Core Components

The Central Processing Unit (CPU) is the heart of a computer, responsible for executing programs and managing system operations. Its efficiency in performing these tasks is largely dependent on the interplay between its core components: the Arithmetic Logic Unit (ALU), the Control Unit (CU), and Registers. Each of these components has a specialized role that contributes to the overall functioning of the CPU and, by extension, the computer itself.

## Arithmetic Logic Unit (ALU)

The ALU is a fundamental component of the CPU that performs all arithmetic and logical operations. Arithmetic operations include basic mathematical functions like addition, subtraction, multiplication, and division, while logical operations involve comparison operations such as AND, OR, NOT, XOR, comparisons of equality, and greater than/less than decisions. The ALU is crucial for the execution of algorithms and processing of data, making it indispensable for the computational aspect of computer operations. The efficiency and speed of the ALU directly impact the CPU's overall performance, especially for tasks requiring complex mathematical computations or logical decision making.

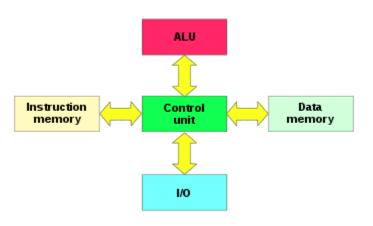

## Control Unit (CU)

The Control Unit orchestrates the operations of the CPU and, by extension, the computer as a whole. It does not execute program instructions; rather, it directs other components of the system to do so. The CU fetches instructions from the computer's memory, decodes them to understand the required actions, and then executes these instructions by coordinating the data flow between the CPU's other components, such as the ALU, registers, and memory. It ensures that the instructions are executed in the correct sequence and at the right time, effectively managing the execution cycle and controlling the flow of data within the CPU. The CU plays a pivotal role in maintaining the organized and efficient operation of the computer's processing capabilities.

Block Diagram of the Control Unit

## Registers

Registers are small, high-speed storage locations directly within the CPU used to hold temporary data and instructions that are being processed by the CPU. There are several types of registers, each serving a specific function:

• **General-purpose** registers can hold both data and addresses (i.e., locations of data in memory), and their use is largely determined by the instruction set architecture (ISA) of the CPU.

- **Special-purpose** registers have specific functions, such as the Program Counter (PC) that holds the address of the next instruction to be executed, or the Instruction Register (IR) that holds the currently executing instruction.

- **Status** registers indicate the current state of the processor, including condition flags that result from the execution of instructions, such as carry, zero, or overflow flags.

Registers provide the CPU with quick access to data and instructions, significantly speeding up the processing by reducing the need to access slower main memory. The number and type of registers, along with how they are utilized by the CPU, can greatly affect the efficiency and performance of a computer system.

Together, the ALU, CU, and registers form an intricate system that allows the CPU to execute complex instructions and process data efficiently. Their coordinated operation is essential for the performance of computing tasks, from simple calculations to complex problem-solving across various applications.

## Instruction Cycle

The Instruction Cycle, also known as the Fetch-Decode-Execute Cycle, is the fundamental process through which a CPU operates and processes commands. This cycle is the heart of a computer's functionality, allowing it to perform tasks, execute

programs, and process data. Understanding this cycle is key to grasping how computers work at a fundamental level.

## Fetch-Decode-Execute Cycle

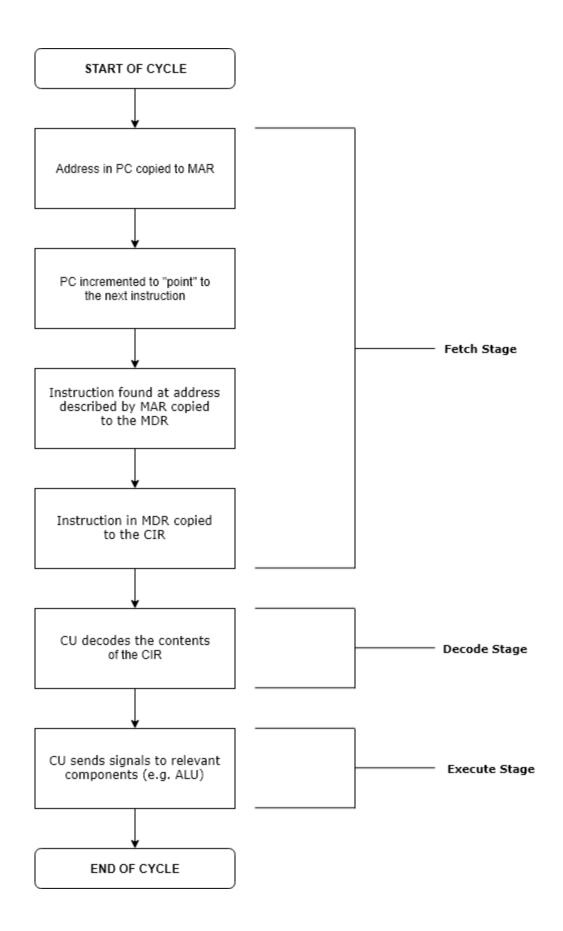

The cycle consists of three main stages:

- Fetch: The first step involves retrieving an instruction from the program memory. The Control Unit (CU) uses the Program Counter (PC) to keep track of which instruction is to be executed next. The PC points to the memory address of the next instruction, which is then fetched from memory and moved into the Instruction Register (IR). After fetching, the PC is updated to point to the following instruction in the sequence, preparing it for the next cycle.

- 2. **Decode:** During this phase, the fetched instruction in the IR is decoded by the CU. Decoding involves translating the binary instruction code into a signal that the CPU can understand and act upon. This process determines what type of operation is to be performed (e.g., arithmetic, logic, data transfer) and which operands (e.g., registers, memory addresses) are involved.

- 3. **Execute:** The final step is where the action specified by the instruction is carried out. This could involve the ALU performing arithmetic or logical operations, the CU directing data to be moved from one location to another, or the CPU interfacing with input/output devices. Once the execution is complete, the CPU moves on to the next instruction in the cycle, starting again with the fetch phase.

#### Pipelining

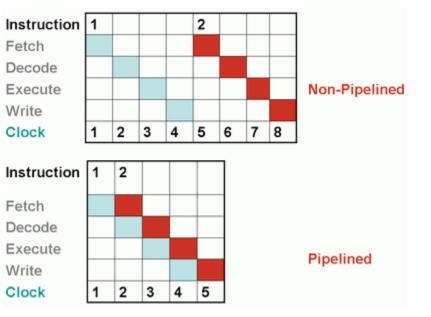

To increase efficiency and the rate at which instructions are processed, modern CPUs employ a technique known as pipelining. Pipelining allows multiple instructions to be at different stages of the instruction cycle simultaneously, akin to an assembly line in a factory. This means that while one instruction is being decoded, another can be fetched, and a third can be executed. The result is a significant increase in the throughput of the CPU - that is, the number of instructions it can process in a given time frame.

Pipelining achieves this efficiency by dividing the fetch-decode-execute process into separate stages with different units within the CPU handling each stage. Each unit operates in parallel with the others, working on different instructions. This overlap ensures that the CPU's various parts are utilized as efficiently as possible, minimizing idle time and maximizing performance.

However, pipelining also introduces complexity in managing the flow of instructions and handling dependencies between them (when one instruction depends on the result of another). Techniques such as instruction reordering, speculative execution, and branch

prediction are used to mitigate these issues, further optimizing the pipeline's efficiency.

The combination of the Fetch-Decode-Execute Cycle and pipelining forms the backbone of CPU operation, enabling modern computers to perform billions of instructions per second, powering everything from basic computing tasks to advanced scientific simulations.

## **Clock Speed and Performance**

The performance of a Central Processing Unit (CPU), which is crucial for the overall speed and efficiency of a computer, is influenced by several factors. Among these, clock speed and core count stand out as primary determinants of how fast a CPU can execute tasks. Understanding these elements, along with other factors like cache size and instruction set architecture, provides insight into the complex nature of CPU performance.

### **Clock Speed**

Clock speed, measured in gigahertz (GHz), indicates the frequency at which a CPU's clock generates pulses. Each pulse or cycle allows the CPU to perform an operation, such as executing an instruction or accessing memory. Essentially, the clock speed determines how many instructions a CPU can process in a second; higher clock speeds typically mean the CPU can perform more operations per second, leading to faster processing and a more responsive computer.

However, clock speed is not the sole determinant of performance. Modern CPUs accomplish tasks more efficiently through advancements in architecture, not just by increasing the clock speed. This is partly because higher clock speeds can lead to increased power consumption and heat generation, which are practical limits to how fast CPUs can run.

### Core Count

The core count of a CPU refers to the number of independent processing units (cores) within a single computing component (chip). Each core can execute instructions as if it were a separate processor, allowing for parallel processing of multiple tasks. This capability significantly enhances performance, especially for applications designed to take advantage of multiple cores through multithreading or multiprocessing.

In practice, doubling the core count does not exactly double the performance due to factors like task parallelizability and overheads from coordinating between cores. Nevertheless, for tasks that can be efficiently divided and executed in parallel, having more cores can dramatically improve processing speed and system responsiveness.

### Performance Factors Beyond Clock Speed

Several other factors affect CPU performance, highlighting that sheer clock speed or core count alone does not define the capabilities of a CPU:

- **Cache Size:** CPUs come with a small amount of very fast memory called cache, used to store copies of frequently accessed data and instructions. Larger caches reduce the need to fetch data from slower main memory, speeding up execution.

- Instruction Set Architecture (ISA): The design of the CPU's instruction set can impact how efficiently it processes instructions. Some architectures are designed for simplicity and high throughput, while others prioritize complex instructions that can accomplish more in a single step.

- **Pipelining and Other Architectural Features:** Modern CPUs use techniques like pipelining to process multiple instruction steps simultaneously, increasing the effective instruction throughput beyond what clock speed alone would suggest.

- **Thermal and Power Management:** CPUs can reduce their clock speed to prevent overheating or to conserve power, affecting performance. Advanced thermal and power management technologies can help maintain higher performance levels for longer periods.

Ultimately, CPU performance is the result of a complex interplay between these and other factors, engineered to balance speed, efficiency, and power consumption. When evaluating CPUs, considering the combination of these characteristics is crucial for understanding their true performance potential in various computing environments.

## Data and Instruction Parallelism

In the realm of computer architecture and processing, parallelism refers to the ability of a computer to perform multiple operations or tasks simultaneously. This concept is key to increasing computational speed and efficiency, especially as the demand for processing power grows with advancements in technology and software complexity. Parallelism can be broadly categorized into two main types: data parallelism and instruction parallelism. Both approaches aim to enhance the performance and throughput of computing systems but do so in different ways.

#### Data Parallelism

Data parallelism involves performing the same operation on multiple data points simultaneously. This approach is particularly effective in tasks where the same set of instructions needs to be executed on a large set of data. For example, in image processing, the same filter might be applied to each pixel of an image; data parallelism allows for the filter to be applied to many pixels at once, significantly speeding up the process.

Modern CPUs with multiple cores can achieve data parallelism by distributing the data across different cores, where each core processes a subset of the data in parallel with the others. Additionally, specialized processors like Graphics Processing Units (GPUs) are designed to excel at data parallelism, capable of handling thousands of such operations concurrently due to their large number of cores optimized for parallel data processing.

#### **Instruction Parallelism**

Instruction parallelism, on the other hand, focuses on executing multiple instructions at the same time. This can be achieved within a single processor by employing techniques such as pipelining, where different stages of instruction execution (fetch, decode, execute, etc.) are performed in an assembly line manner for different instructions. Superscalar architecture takes this further by allowing multiple instructions to enter the pipeline simultaneously, enhancing throughput.

Another aspect of instruction parallelism is achieved through the use of multiple processing units (cores) within a single CPU. In such multi-core processors, different cores can execute different instructions concurrently, further contributing to the system's overall computational speed. This method is particularly beneficial for multi-threaded applications where the program is designed to execute different parts of its code in parallel.

#### Combining Data and Instruction Parallelism

High-performance computing systems often combine data and instruction parallelism to maximize efficiency and processing power. This combination is especially prevalent in scientific computing, data analysis, and real-time processing tasks, where large datasets and complex algorithms require substantial computational resources.

For instance, a multi-core CPU might employ instruction parallelism by distributing different tasks across its cores, while each core may utilize data parallelism to process multiple data elements of its task simultaneously. Similarly, GPUs leverage their architecture to perform a vast number of simple data operations in parallel, making them ideal for tasks that can be broken down into smaller, repetitive operations.

In conclusion, data and instruction parallelism are fundamental concepts in modern computing, allowing for the simultaneous execution of multiple instructions and processing of multiple data points. By leveraging these forms of parallelism, computing systems can achieve higher levels of performance and efficiency, meeting the demands of complex applications and large-scale data processing.